#### FEATURES

Full evaluation kit for the ADM1073 hot swap controller Kit contains two boards:

Main evaluation board for bench evaluation Micro evaluation board to drop into user's system Both boards feature:

On-board FET to control load current Programmable current limit levels (value of R<sub>SENSE</sub>) Programmable operating voltage range (R1–R4 resistors) Choice of default or custom timing values LEDs on all logic inputs and outputs

Pushbuttons for asserting logic inputs

Main evaluation board features:

Banana connectors for connecting power and loads Edge connectors allow simulation of real hot swap events External signals can be switched in through SMB

connectors to overide  $V_{IN}$ , SENSE, and UV/OV signals

Opto-isolators for logic inputs and outputs Micro evaluation board feature:

Drops into a user's system, replacing the current hot swap device

#### MAIN EVALUATION KIT CONTENTS

Main evaluation board Micro evaluation board ADM1073 data sheet EVAL-ADM1073EB evaluation kit data sheet 5 ADM1073 samples

#### **MICRO EVALUATION KIT CONTENTS**

Micro evaluation board ADM1073 data sheet EVAL-ADM1073EB evaluation kit data sheet 5 ADM1073 samples

#### **GENERAL DESCRIPTION**

This evaluation kit allows the ADM1073 negative-voltage hot swap controller to be easily evaluated. The ADM1073 provides undervoltage and overvoltage protection by monitoring the supply voltage, and robust current limiting by monitoring the load current. The device uses a FET in the power path to control the load current.

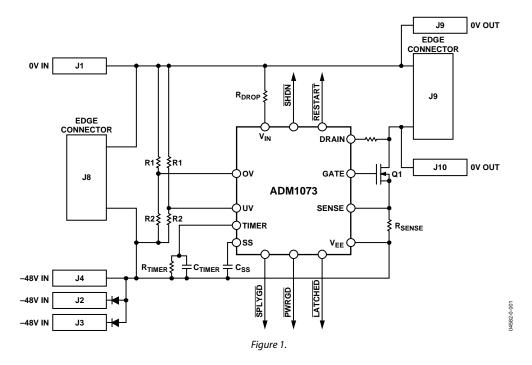

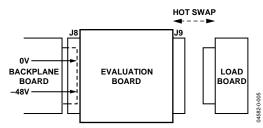

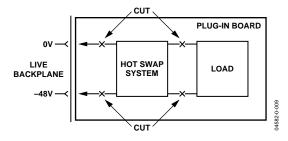

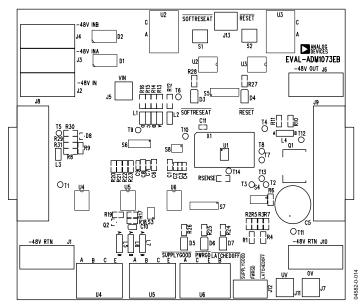

#### MAIN EVALUATION BOARD FUNCTIONAL BLOCK DIAGRAM

#### Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.326.8703

© 2004 Analog Devices, Inc. All rights reserved.

# **TABLE OF CONTENTS**

| Evaluation Board Hardware                    | 3  |

|----------------------------------------------|----|

| Important                                    | 3  |

| Connector, Switch, Jumper, and LED Functions | 3  |

| Operating the Main Evaluation Board          | 8  |

| ADM1073 Residing on a Plug-In Board          | 8  |

| ADM1073 Residing on a Backplane              | 9  |

| Load Board                                   | 9  |

| Backplane Board                              | 9  |

| Setting up the Main Evaluation Board1        | .0 |

#### **REVISION HISTORY**

9/04—Revision 0: Initial Version

| Operating the Micro Evaluation Board11                    |

|-----------------------------------------------------------|

| Setting up the Micro Evaluation Board11                   |

| Integrating the Micro Evaluation Board into the System 12 |

| Evaluation Board Schematics                               |

| Ordering Information                                      |

| Main Evaluation Board Bill of Materials16                 |

| Micro Evaluation Board Bill of Materials17                |

| Ordering Guide                                            |

### **EVALUATION BOARD HARDWARE**

#### IMPORTANT

Take the following precautions, when using the EVAL-ADM1073EB evaluation kit under high voltage conditions:

- Do not work alone.

- Always keep one hand in your pocket or behind your back when around a high voltage system.

- Wear footwear with a rubber bottom.

- Wear eye protection (safety goggles).

- Do not wear any jewelry or other articles that could accidentally contact circuitry and conduct current.

- Work on an antistatic mat.

- Set up your work area away from possible grounds that you might accidentally contact.

- Connect/disconnect any test leads with the power off and the equipment unplugged. Use clip leads or solder temporary wires to reach difficult-to-access locations.

- Perform as many tests as possible with the power off and the equipment unplugged.

- After tests have been performed with the power applied, turn off the power and disconnect the power supply from the board.

- Fully discharge large load capacitors with an appropriate resistor.

#### CONNECTOR, SWITCH, JUMPER, AND LED FUNCTIONS

| Tabl | e 1. Connec | tor Functions |

|------|-------------|---------------|

|      |             |               |

| Pin | Name    | Function                                                                                                                                                                      |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J1  | -48VRTN | Black Banana Connector. –48 V return input voltage line.                                                                                                                      |

| J2  | -48VIN  | Blue Banana Connector. –48 V input voltage line.                                                                                                                              |

| J3  | -48VIN  | Blue Banana Connector. –48 V input voltage line (diode OR'ed with J4 input).                                                                                                  |

| J4  | -48VIN  | Blue Banana Connector. –48 V input voltage line (diode OR'ed with J3 input).                                                                                                  |

| J5  | VIN     | SMB Connector. V <sub>IN</sub> voltage can be monitored via J5.                                                                                                               |

| J6  | -48VOUT | Blue Banana Connector. –48 V output voltage line.                                                                                                                             |

| J7  | UV      | SMB Connector. UV voltage can be monitored or applied via J5.                                                                                                                 |

| J8  |         | Edge Connector. Allows connection of a backplane board for powering the board and simulating hot swap events.                                                                 |

| J9  |         | Edge Connector. Allows connection of a load board for simulating hot swap events.                                                                                             |

| J10 | -48VRTN | Black Banana Connector. –48 V return output voltage line.                                                                                                                     |

| J11 | OV      | SMB Connector. OV voltage can be monitored or applied via J11.                                                                                                                |

| J12 |         | SPLYGD, PWRGD, and LATCHED outputs can monitored via J12.                                                                                                                     |

|     |         | J12-1: Feed SPLYGD to J12-1 by closing S7-3 switch.                                                                                                                           |

|     |         | J12-2: Feed PWRGD to J12-2 by closing S7-6 switch.                                                                                                                            |

|     |         | J12-3: Feed LATCHED to J12-3 by closing S7-9 switch.                                                                                                                          |

| J13 |         | SHDN and RESTART inputs can be applied or monitored via J13.                                                                                                                  |

|     |         | J13-1: Feed SHDN to J13-1 by closing S5-6 switch.                                                                                                                             |

|     |         | J13-2: Feed RESTART to J13-2 by closing S5-2 switch.                                                                                                                          |

| J14 |         | Allows an external voltage to be applied to overdrive the SS pin. This alters the internal current limit reference voltage, which, in effect, alters the current limit level. |

|     |         | J14-1: Applies SS voltage to this terminal.                                                                                                                                   |

|     |         | J14-2: ADM1073 V <sub>EE</sub> voltage.                                                                                                                                       |

#### Table 2. Switch Functions

| Switch     | Description                                           | Position     | Function                                              | Default |

|------------|-------------------------------------------------------|--------------|-------------------------------------------------------|---------|

| S1         | Pushbutton switch for driving RESTART pin (via S5-1)  | N/A          | Active-low pulse sent to pin when button is depressed | N/A     |

| S2         | Pushbutton switch for driving SHDN pin (via S5-5)     | N/A          | Active-low pulse sent to pin when button is depressed | N/A     |

| S3         |                                                       |              |                                                       |         |

| S3-1       | Connects R18 to V <sub>IN</sub> pin                   | Closed       | Base of FET Q2 connected to $V_{IN}$ pin              | Open    |

|            |                                                       | Open         | Base of FET Q2 unconnected                            |         |

| S3-2       | Connects R17 to V <sub>IN</sub> pin                   | Closed       | Emitter of FET Q2 connected to V <sub>IN</sub> pin    | Open    |

|            |                                                       | Open         | Emitter of FET Q2 unconnected                         |         |

| S3-3       | Connects PWRGD pin to links L6 and L7                 | Closed       | PWRGD pin connected to L6, L7                         | Open    |

| _          |                                                       | Open         | PWRGD pin not connected to U5                         |         |

| S3-4       | Unused                                                |              |                                                       |         |

| S4         |                                                       |              |                                                       |         |

| S4-1       | Connects midpoint of R1/R2 resistor divider to OV pin | Closed       | R1/R2 node connected to OV pin                        | Closed  |

| 64.2       | Comports D1/D2/D2 register not york to OV nin         | Open         | R1/R2 node disconnected                               | 0.000   |

| S4-2       | Connects R1/R2/R3 resistor network to OV pin          | Closed       | R1/R2/R3 node connected to OV pin                     | Open    |

| S4-3       | Connects J11 to OV pin                                | Open<br>Open | R1/R2/R3 node disconnected<br>J11 connected to OV pin | Onon    |

| 34-3       | Connects of 1 to OV pin                               | Closed       | J11 disconnected                                      | Open    |

| S4-4       | Connects midpoint of R1/R2 resistor divider to UV pin | Closed       | R1/R2 node connected to UV pin                        | Closed  |

| 7-4        |                                                       | Open         | R1/R2 node disconnected                               | Closed  |

| S4-5       | Connects R1/R2/R3 resistor network to UV pin          | Closed       | R1/R2/R3 node connected to OV pin                     | Open    |

| 54 5       | connects m/n2/n5 resistor network to ov pin           | Open         | R1/R2/R3 node disconnected                            | open    |

| S4-6       | Connects J11 to OV pin                                | Open         | J11 connected to OV pin                               | Open    |

| 510        |                                                       | Closed       | J11 disconnected                                      | open    |

| <b>S</b> 5 |                                                       |              |                                                       |         |

| S5-1       | Connects LED D3 to RESTART pin                        | Closed       | D3 connected to RESTART pin                           | Closed  |

|            |                                                       | Open         | D3 disconnected                                       |         |

| S5-2       | Connects pushbutton switch S1 to RESTART pin          | Closed       | S1 connected to RESTART pin                           | Closed  |

|            |                                                       | Open         | S1 disconnected                                       |         |

| S5-3       | Connects J13-2 to the RESTART pin                     | Closed       | J13 connected to RESTART pin                          | Open    |

|            | ·                                                     | Open         | J13 disconnected                                      |         |

| S5-4       | Connects opto-isolator U2 to RESTART pin              | Closed       | U2 connected to RESTART pin                           | Open    |

|            |                                                       | Open         | U2 disconnected                                       |         |

| S5-5       | Connects LATCHED output to RESTART input              | Closed       | Both pins connected                                   | Open    |

|            |                                                       | Open         | Both pins disconnected                                |         |

| S5-6       | Connects LED D4 to SHDN pin                           | Closed       | D4 connected to SHDN pin                              | Closed  |

|            |                                                       | Open         | D4 disconnected                                       |         |

| S5-7       | Connects pushbutton switch S2 to SHDN pin             | Closed       | S1 connected to SHDN pin                              | Closed  |

|            |                                                       | Open         | S1 disconnected                                       | closed  |

| S5-8       | Connects J13-1 to SHDN pin                            | Closed       | J13 connected to SHDN pin                             | Open    |

|            |                                                       | Open         | J13 disconnected                                      |         |

| S5-9       | Connects opto-isolator U3 to SHDN pin                 | Closed       | U2 connected to SHDN pin                              | Open    |

|            |                                                       | Open         | U2 disconnected                                       |         |

| S5-10      | Connects LATCHED output to SHDN input                 | Closed       | Both pins connected                                   | Open    |

| 23 10      |                                                       | Open         | Both pins disconnected                                |         |

|            |                                                       | Open         | both pins disconnected                                |         |

| Switch       | Description                                        | Position       | Function                     | Default |

|--------------|----------------------------------------------------|----------------|------------------------------|---------|

| S6           |                                                    |                |                              |         |

| S6-1         | Connects user TIMER capacitor (C6) to TIMER pin    | Closed         | C6 connected to TIMER pin    | Open    |

|              |                                                    | Open           | C6 disconnected pin          |         |

| S6-2         | Connects default TIMER capacitor (C7) to TIMER pin | Closed         | C7 connected to TIMER pin    | Closed  |

|              |                                                    | Open           | C7 disconnected pin          |         |

| S6-3         | Connects large TIMER capacitor (C8) to TIMER pin   | Closed         | C8 connected to TIMER pin    | Open    |

|              |                                                    | Open           | C8 disconnected pin          | -       |

| S6-4         | Connects small TIMER capacitor (C9) to TIMER pin   | Closed         | C9 connected to TIMER pin    | Open    |

|              |                                                    | Open           | C9 disconnected pin          | -       |

| S6-5         | Connects small TIMER resistor (R23) to TIMER pin   | Closed         | R23 connected to TIMER pin   | Open    |

|              |                                                    | Open           | R23 disconnected             | -       |

| S6-6         | Connects large TIMER resistor (R22) to TIMER pin   | Closed         | R22 connected to TIMER pin   | Open    |

|              |                                                    | Open           | R22 disconnected             |         |

| S6-7         | Connects default TIMER resistor (R21) to TIMER pin | Closed         | R21 connected to TIMER pin   | Open    |

|              |                                                    | Open           | R21 disconnected             |         |

| S6-8         | Connects user TIMER resistor (R20) to TIMER pin    | Closed         | R20 connected to TIMER pin   | Open    |

|              |                                                    | Open           | R20 disconnected             |         |

| S7           |                                                    |                |                              |         |

| S7-1         | Connects LED D5 to SPLYGD pin                      | Closed         | LED D5 enabled               | Closed  |

|              |                                                    | Open           | LED D5 disabled              |         |

| S7-2         | Connects opto-isolator U4 to SPLYGD pin            | Closed         | U4 connected to SPLYGD pin   | Open    |

|              |                                                    | Open           | U4 disconnected              | open    |

| S7-3         | Connects J12-1 to SPLYGD pin                       | Closed         | J12 connected to SPLYGD pin  | Open    |

| 57 5         |                                                    | Open           | J12 disconnected             | open    |

| S7-4         | Connects LED D6 to PWRGD pin                       | Closed         | LED D6 enabled               | Closed  |

| J/-4         | connects LED Do to 1 which pin                     | Open           | LED D6 disabled              | Closed  |

| S7-5         | Connects opto-isolator U5 to PWRGD pin             | Closed         | U5 connected to PWRGD pin    | Open    |

| 37-3         |                                                    |                | U5 disconnected              | Open    |

| 67.6         |                                                    | Open<br>Closed |                              | 0.000   |

| S7-6         | Connects J12-2 to PWRGD pin                        |                | J12 connected to PWRGD pin   | Open    |

| <b>~ - -</b> |                                                    | Open           | J12 disconnected             |         |

| S7-7         | Connects LED D7 to LATCHED pin                     | Closed         | LED D7 enabled               | Closed  |

|              |                                                    | Open           | LED D7 disabled              |         |

| S7-8         | Connects opto-isolator U6 to LATCHED pin           | Closed         | U6 connected to LATCHED pin  | Open    |

|              |                                                    | Open           | U6 disconnected              |         |

| S7-9         | Connects J12-3 to LATCHED pin                      | Closed         | J12 connected to LATCHED pin | Open    |

|              |                                                    | Open           | J12 disconnected             |         |

| S7-10        | Not connected                                      | N/A            | N/A                          | N/A     |

| S8           |                                                    |                |                              |         |

| S8-1         | Connects small SS capacitor (C4) to SS pin         | Closed         | C4 connected to SS pin       | Open    |

|              |                                                    | Open           | C4 disconnected              |         |

| S8-2         | Connects large SS capacitor (C3) to SS pin         | Closed         | C3 connected to SS pin       | Open    |

|              |                                                    | Open           | C3 disconnected              |         |

| S8-3         | Connects default SS capacitor (C2) to SS pin       | Closed         | C2 connected to SS pin       | Closed  |

|              |                                                    | Open           | C2 disconnected              |         |

| S8-4         | Connects user SS capacitor (C1) to SS pin          | Closed         | C1 connected to SS pin       | Open    |

|              |                                                    | Open           | C1 disconnected              |         |

#### Table 3. Jumper Functions

| Switch | Description                              | Default In/Out |  |  |

|--------|------------------------------------------|----------------|--|--|

| L1     |                                          |                |  |  |

| L1-A   | Connects R13 to V <sub>IN</sub> pin      | Out            |  |  |

| L1-A   | Connects R14 to V <sub>IN</sub> pin      | Out            |  |  |

| L1-A   | Connects R15 to V <sub>IN</sub> pin      | Out            |  |  |

| L1-A   | Connects R16 to V <sub>IN</sub> pin      | Out            |  |  |

| L2     | Connects R12 to V <sub>IN</sub> pin      | In             |  |  |

| L3     | Connects driver circuit for all LEDs     | In             |  |  |

| L4     |                                          |                |  |  |

| L4-A   | Connects R11 to DRAIN pin                | In             |  |  |

| L4-A   | Connects R10 to DRAIN pin                | Out            |  |  |

| L5     |                                          |                |  |  |

| L5-A   | Connects Pin 1 of U5 to external circuit | Out            |  |  |

| L5-A   | Connects Pin 1 of U5 to patchwork        | In             |  |  |

| L6     |                                          |                |  |  |

| L6-A   | Connects Pin 6 of U5 to external circuit | Out            |  |  |

| L6-A   | Connects Pin 6 of U5 to patchwork        | In             |  |  |

| L7     |                                          |                |  |  |

| L7-A   | Connects Pin 5 of U5 to external circuit | Out            |  |  |

| L7-A   | Connects Pin 5 of U5 to patchwork        | In             |  |  |

#### Table 4. LED Functions

| LED                                                                                                           | Name    | Function                                                                                                                 |  |  |

|---------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| D3 RESTART Indicates when an active-low pulse is asserted on the RESTART input. This yellow LED turns on when |         |                                                                                                                          |  |  |

|                                                                                                               |         | low, indicating that a soft reseat event has been initiated. Use Switch S5 to set different methods of driving RESTART.  |  |  |

|                                                                                                               |         | Note: S13-1 must be closed to enable this LED.                                                                           |  |  |

| D4                                                                                                            | SHDN    | Indicates when an active-low pulse is asserted on the SHDN input. This yellow LED is on when the line is driven low,     |  |  |

|                                                                                                               |         | indicating that a reset event has been initiated. Use Switch S5 to set different methods of driving SHDN.                |  |  |

|                                                                                                               |         | Note: S13-6 must be closed to enable this LED.                                                                           |  |  |

| D5                                                                                                            | SPLYGD  | Indicates when the active-low SPLYGD output is asserted. This green LED turns on when the line is driven low, indicating |  |  |

|                                                                                                               |         | that the supply voltage is inside the programmed operating range.                                                        |  |  |

|                                                                                                               |         | Note: S7-1 must be closed to enable this LED.                                                                            |  |  |

| D6                                                                                                            | PWRGD   | Indicates when the active-low PWRGD output is asserted. This green LED turns on when the line is driven low, indicating  |  |  |

|                                                                                                               |         | that the load capacitance has been fully charged and the output voltage is at its full potential.                        |  |  |

|                                                                                                               |         | Note: S7-4 must be closed to enable this LED.                                                                            |  |  |

| D7                                                                                                            | LATCHED | Indicates when the active-low LATCHED output is asserted. This red LED turns on when the line is driven low, indicating  |  |  |

|                                                                                                               |         | that a current fault has caused the ADM1073 to latch off.                                                                |  |  |

|                                                                                                               |         | Note: S7-7 must be closed to enable this LED.                                                                            |  |  |

#### Table 5. Testpoints

| Testpoint | Function                                                                                                                                                                                                                                                                        |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T1        | Monitors the -48VRTN line. This voltage is typically 48 V above the -48VIN rail and VEE. This line can be considered an input and output line.                                                                                                                                  |

| T2        | Monitors the voltage on the ADM1073 OV (overvoltage) pin.                                                                                                                                                                                                                       |

| Т 3       | Monitors the voltage on the ADM1073 UV (undervoltage) pin.                                                                                                                                                                                                                      |

| T4        | Monitors the -48 V input line. This voltage is tied to ADM1073 ground (VEE pin).                                                                                                                                                                                                |

| Т5        | Monitors the -48 V input line. This voltage is tied to ADM1073 ground (VEE pin).                                                                                                                                                                                                |

| Т6        | Monitors the V <sub>IN</sub> pin. This voltage is typically 12 V above the −48VIN rail and V <sub>EE</sub> .                                                                                                                                                                    |

| Т7        | Monitors the GATE pin. This voltage is 12 V under normal operating conditions.                                                                                                                                                                                                  |

| Т8        | Monitors the DRAIN pin, which is used for linear current foldback.                                                                                                                                                                                                              |

| Т9        | Monitors the TIMER pin, which is used to control the on-time of the retry function.                                                                                                                                                                                             |

| T10       | Monitors the SS pin, which is used to control the soft start ramp rate.                                                                                                                                                                                                         |

| T11       | Monitors the -48VRTN line. This voltage is typically 48 V above the -48VIN rail and VEE. This line can be considered an input and output line.                                                                                                                                  |

| T12       | Monitors the -48 V output line. This node is also connected to the FET DRAIN pin and DRAIN resistor.                                                                                                                                                                            |

| T13       | Monitors the –48 V input voltage/ADM1073 V <sub>EE</sub> voltage close to the SENSE resistor. The V <sub>EE</sub> to SENSE voltage is the voltage across the sense resistor. A probe across T13 and T14 gives an accurate measurement of the voltage across the sense resistor. |

| T14       | Monitors the SENSE voltage. The $V_{EE}$ to SENSE voltage is the voltage across the SENSE resistor. This node is also the source pin of the pass FET. A probe across T13 and T14 gives an accurate measurement of the voltage across the SENSE resistor.                        |

| T15       | Monitors the voltage on the FET source voltage.                                                                                                                                                                                                                                 |

| T16       | Monitors the voltage on the LATCHED input.                                                                                                                                                                                                                                      |

| T17       | Monitors the voltage on the PWRGD input.                                                                                                                                                                                                                                        |

| T18       | Monitors the voltage on the SPLYGD input.                                                                                                                                                                                                                                       |

### **OPERATING THE MAIN EVALUATION BOARD**

Many tests and hot swap scenarios can be modeled on the EVAL-ADM1073EB main evaluation board:

- Powering up into a load (resistive, capacitive, RC combination); successful hot swap

- Powering up, then applying a load (resistive, capacitive, RC combination); successful hot swap

- Powering up into a shorted output

- Powering up, then shorting the output

- Permanent overcurrent fault

- Temporary overcurrent fault

- Temporary overcurrent fault followed by a permanent overcurrent fault

- Three distinct levels of overcurrent fault (see the ADM1073 data sheet)

- Overvoltage condition

- Undervoltage condition

All tests involving shorts can be simulated with the ADM1073 residing on either the plug-in module/board side or the back-plane side. The main evaluation board can be configured to recreate the two ways in which the ADM1073 can be used in a real system.

#### ADM1073 RESIDING ON A PLUG-IN BOARD

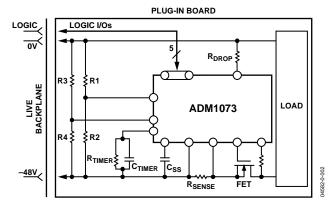

Typically, the ADM1073 and its accompanying components are mounted on a plug-in board. This board is then slotted into the live backplane, when required. When the power lines connect, the ADM1073 powers up. If the supply is stable and within tolerance, it turns the FET on in a controlled manner, applying power safely to the load and powering up the rest of the board.

Figure 2. ADM1073 Residing on a Plug-In Module

To evaluate the ADM1073 residing on a plug-in board, set up the evaluation board as follows:

- 1. Set up the board with the preferred load. You can connect the load to the board in several ways:

- If a single load component is sufficient, you can solder the component directly onto the evaluation board in the C4 position.

- You can custom-build a board to simulate a plug-in module's load and plug it into Edge Connector J9. (See Figure 8 for a schematic of the J9 pin diagram.)

- Connect a load via Connectors J6 and J10.

- If a no-load condition is required, do not connect anything to J6, J9, or J10, and do not solder any additional load components to the evaluation board.

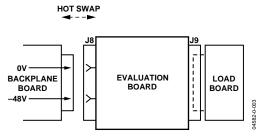

Figure 3. Evaluation Board Simulating the Setup in Figure 1

- 2. Apply power to the board via leads connected directly to a power supply. Power is normally applied through the black and blue banana connectors (J1 to J4). Connect the higher potential (RTN or 0 V) to Socket J1 (black). Connect the lower potential of the supply to J2 or J3 (blue). A diode OR'ing scheme is employed at these terminals, so that two supplies can be applied simultaneously, if required. In this situation, the supply with the higher potential is used. If this supply potential drops below the voltage of the second redundant supply, then the board switches over to the second supply. To bypass the diodes, connect a single power supply to the board via Socket J2 (blue).

- 3. To recreate a live insertion event, either turn on the power supply or make the connection to the live supply. Take the proper safety precautions when applying live voltages to the evaluation board.

- 4. You can also apply power to the board via Connector J8. A simple backplane board can be constructed that plugs into Connector J8 and provides the -48 V supply. You can now simulate a live insertion event by plugging the backplane board (see the Backplane Board section) with a live negative supply into Connector J8.

- 5. To simulate a reseating event, disconnect the evaluation board and backplane boards and reconnect them while the supply is live. This corresponds to manually reseating a plug-in module. This method recreates a board insertion and/or removal scenario more accurately, because the plugging or unplugging of a board from a live supply triggers the ADM1073 to respond. Again, take the proper precautions when connecting live voltages to the evaluation board.

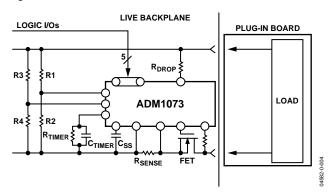

#### **ADM1073 RESIDING ON A BACKPLANE**

The ADM1073 can perform similar undervoltage and overvoltage protection and current limiting functions when placed on the backplane itself.

This type of setup can be recreated with the ADM1073 evaluation board. Power can be applied through a backplane board or with power leads, as described in the ADM1073 Residing on a Plug-In Board section. The power supply and the evaluation board should be connected together by either method, and the power applied (Figure 4). This unit now represents a live backplane with built-in ADM1073 circuitry in Figure 5.

Figure 4. ADM1073 Residing on a Backplane

Figure 5. Evaluation Board Simulating the Setup in Figure 3

To simulate a live insertion event with the ADM1073 residing on the backplane:

- 1. Connect the load to the evaluation board via Connector J9, or J9 and J10, as described in the ADM1073 Residing on a Plug-In Board section.

- 2. To represent reseating, disconnect and reconnect the load from/to the evaluation board.

Note that the ADM1073 can be employed on both the plug-in board/module and the backplane sides of a system. This provides the system with double protection.

#### LOAD BOARD

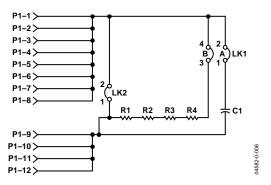

Figure 6 is a diagram of a load board that emulates the load on a plug-in module and connects to Connector J9. This board contains a series resistance and capacitance connected in parallel. A set of jumpers changes the manner in which the components are applied: resistor only, capacitor only, RC in parallel, or short circuit. The board should be set up via the jumpers before power is applied. For example, to set up the load board to emulate an RC load, place shorting links into both LK1 A and LK1 B jumpers, and leave LK2 open.

Figure 6. Diagram of Load Board

#### **BACKPLANE BOARD**

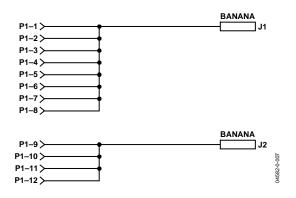

You can also employ a backplane board to emulate the backplane side of your system. This board provides an alternative way of applying power to the ADM1073 evaluation board (instead of using the J1 to J4 power connectors of the evaluation board).

- 1. Insert the backplane board into Edge Connector J8 of the evaluation board to apply power to the board. This might be useful when simulating live insertion and removal events with the ADM1073 evaluation kit, especially when simulating a situation where the ADM1073 resides on a plug-in module.

- 2. To recreate a live insertion event, plug the backplane board (with a live supply) into the evaluation board (Connector J8).

Figure 7. Diagram of Backplane Board

#### SETTING UP THE MAIN EVALUATION BOARD

The evaluation board can have different configurations of supply voltage, operating range, maximum allowable load current, and timing values.

To set up the main evaluation board:

- 1. Choose a shunt resistor. A constant voltage of 12.3 V (above  $V_{EE}$ ) is generated at the  $V_{IN}$  pin via the shunt resistor. A shorting link in Header L2 selects the standard  $R_{DROP}$  of 20 k $\Omega$ . Other resistors and resistor combinations can be selected via header L1. The  $V_{IN}$  voltage can be monitored via Connector J5.

- 2. Choose values for Resistors R1 to R4 to suit the desired operating voltage range and hysteresis levels. The default resistors values (R1/R3 = 39 k $\Omega$ , R2/R4 = 1 k $\Omega$ ) give an operating range of ~34.5 V to ~78 V with hysteresis levels of ~200 mV on UV and OV. You can also use a 3-resistor string (R5 to R7) to set these parameters. Use Switch S4 to apply the preferred network. See the ADM1073 data sheet for other resistor ratios and their operating ranges. Note that 1% accurate resistors should be used for accuracy.

- 3. Choose the maximum load current that is permitted before the ADM1073 registers a current fault. This is determined by the choice of sense resistor,  $R_{SENSE}$  (R6). The evaluation board has a 33 m $\Omega$  sense resistor by default, which sets up a maximum inrush current level of 3.12 A and maximum load current level of 2.61 A.  $R_{SENSE}$  can be changed to alter the load current level (see the ADM1073 datasheet for details). Note that 1% accurate resistors should be used for accuracy.

- 4. Choose a value for the soft start capacitor,  $C_{SS}$ . This capacitor is connected between the SS pin and  $V_{EE}$ . It adjusts the soft start current profile at initial connection. You can switch in different capacitor values via Switch S8 on the evaluation board. See the ADM1073 datasheet for details.

- 5. Choose values for the TIMER capacitor, C<sub>TIMER</sub>, and the TIMER resistor, R<sub>TIMER</sub>. These components set the on-time of the limited consecutive retry scheme. You can switch in different capacitor and resistor values via Switch S6 on the evaluation board. See the ADM1073 datasheet for details.

- 6. Choose the value of the drain resistor required for linear limit foldback via a shorting link in Header L4. The default value of 2.2 M $\Omega$  is selected by a shorting link in Header L4, Position B.

- 7. The evaluation board has an IRF3910 DPAK FET mounted by default. If you want to change this FET, remove the component Q1, and mount a replacement. Note that a triple footprint is present that can accommodate DPAK, D2PAK, and many through-hole FET packages.

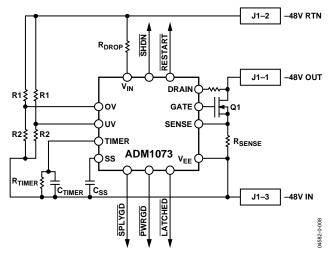

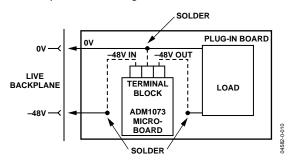

### **OPERATING THE MICRO EVALUATION BOARD**

The EVAL-ADM1073EB evaluation kit contains a second evaluation board, the EVAL-ADM1073EB micro evaluation board, which is designed to drop onto a plug-in module or a backplane, replacing the current hot swap device. The performance of the ADM1073 can then be evaluated within your system.

The micro evaluation board contains a subset of the main evaluation board components :

- On-board FET to control load current

- Programmable operating voltage range (R1 to R4)

- Programmable current limit levels (value of R<sub>SENSE</sub>)

- Programmable soft start ramp (Capacitor C<sub>ss</sub>)

- Programmable TIMER on-time

- LEDs on all logic I/Os

- Pushbutton switches for asserting logic inputs

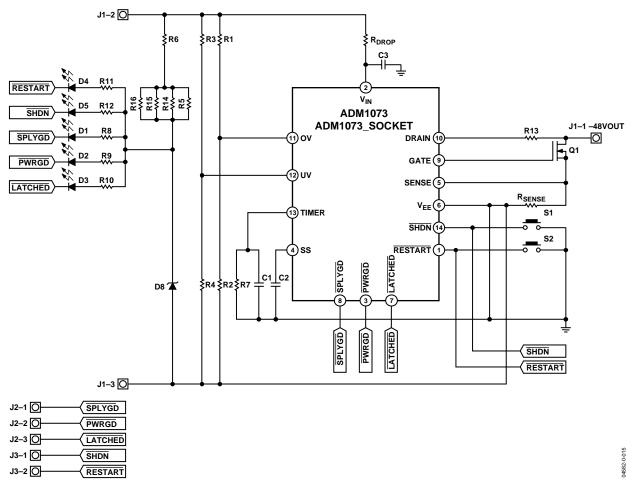

Figure 8. Micro Evaluation Board Functional Block Diagram

By cutting various tracks around the current hot swap device in a user system and soldering the ADM1073 micro evaluation board in position above it, the ADM1073 and its external components can be integrated into the system in place of the original hot swap circuitry. This allows the user to evaluate the ADM1073's performance in the system itself.

#### SETTING UP THE MICRO EVALUATION BOARD

You can set up the micro evaluation board in various configurations, as follows:

- 2. Choose values for Resistors R1 to R4 to suit the desired operating voltage range and hysteresis levels. The default resistors values (R1/R3 =  $39 \text{ k}\Omega$ , R2/R4 =  $1 \text{ k}\Omega$ ) give an operating range of~34.5 V to ~78 V with hysteresis levels of ~200 mV on UV and OV. See the ADM1073 data sheet for other resistor ratios and their operating ranges. Note that 1% accurate resistors should be used for accuracy.

- 3. Choose the maximum load current that is permitted before the ADM1073 registers a current fault. This is determined by the choice of sense resistor,  $R_{SENSE}$  (R6). The evaluation board has a 33 m $\Omega$  sense resistor by default, which sets up a maximum inrush current level of 3.12 A and maximum load current level of 2.61 A.  $R_{SENSE}$  can be changed to alter the load current level. See the ADM1073 datasheet for details. Note that 1% accurate resistors should be used for accuracy.

- 4. Choose a value for the soft start capacitor,  $C_{SS}$ . This capacitor is connected between the SS pin and  $V_{EE}$ . It adjusts the soft start current profile at initial connection. Different value capacitors can be soldered in. See the ADM1073 data sheet for details.

- 5. Choose values for the TIMER capacitor, C<sub>TIMER</sub>, and the TIMER resistor, R<sub>TIMER</sub>. These components set the on-time of the limited consecutive retry scheme. Different capacitor and resistor values can be soldered. See the ADM1073 data sheet for details.

- 6. Choose the value of the drain resistor required for linear limit foldback via a shorting link in Header L4. A default value of  $2.2 \text{ M}\Omega$  is mounted on the micro evaluation board, but you can alter this component, if required.

- 7. The micro evaluation board has an IRF3910 DPAK FET mounted by default. If you want to change this FET, remove the component, Q1, and mount a replacement. Note that a dual footprint is present on the micro evaluation board that can accommodate DPAK and D2PAK packages.

# INTEGRATING THE MICRO EVALUATION BOARD INTO THE SYSTEM

The current system must be modified to disconnect or remove the existing hot swap circuitry and replace it with the micro evaluation board. The following steps describe a situation in which the hot swap circuitry resides on a plug-in module. The same method applies when a backplane-side hot swap system is implemented.

1. Locate the existing hot swap device and its accompanying components and disconnect this portion of the system by cutting the relevant tracks on the board, or alternatively, desoldering and removing the relevant components, as shown in Figure 9.

Figure 9. Removing Existing Hot Swap Circuitry from the System

2. To integrate the micro evaluation board into your system in place of the original hot swap circuitry, clamp three wires into the terminal block, J1, of the micro evaluation board and solder them into position on the board. If you need to access the logic I/Os, there are blank pads on the board that can be used for this purpose. The micro evaluation board now substitutes for the old hot swap circuitry, as shown in Figure 10.

Figure 10. Integrating the Micro Evaluation Board into the System

The micro evaluation board has an insulating coating on its underside to protect the system. If the underside of the board were not protected, shorts could occur on the module or backplane below it.

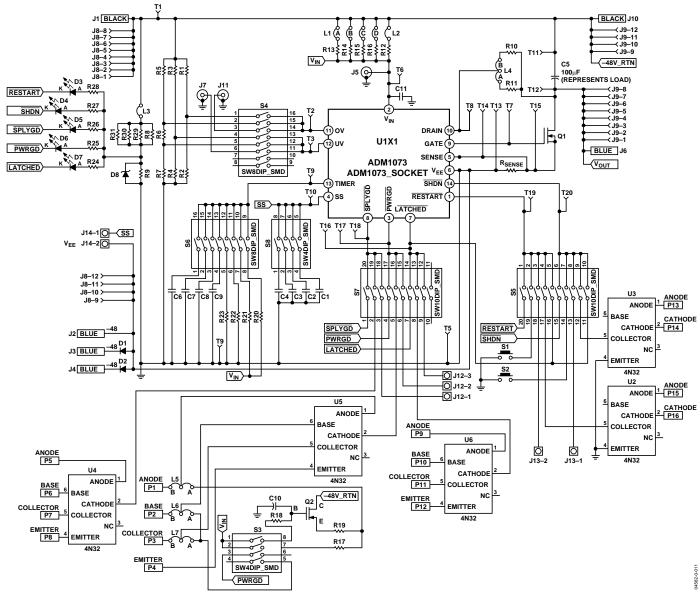

### **EVALUATION BOARD SCHEMATICS**

Figure 11. EVAL-ADM1073EB Evaluation Board Schematic

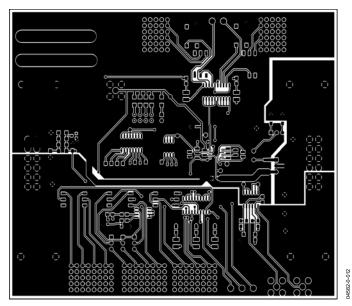

Figure 12. EVAL-ADM1073EB Evaluation Board Component-Side Silkscreen

Figure 13. EVAL-ADM1073EB Evaluation Board Solder-Side Silkscreen

Figure 14. EVAL-ADM1073EB Evaluation Board Component Placement Diagram

Figure 15. EVAL-ADM1073EB Micro Evaluation Board Circuit Diagram

### **ORDERING INFORMATION**

#### MAIN EVALUATION BOARD BILL OF MATERIALS

Table 6.

| Qty    | <b>Ref Description</b> | Part Type                     | Value   | Part Decal     | Part No.          |

|--------|------------------------|-------------------------------|---------|----------------|-------------------|

| 1      | X1                     | ADM1073_SKT                   |         | 14-TSSOP SKT   | OTS14(24)-0.65-01 |

| 1      | U1                     | ADM1073ARU                    |         | 14-TSSOP       | ADM1073           |

| 5      | U2–U6                  | 4N32                          |         | DIP6_SMD       | FEC 359-7830      |

| 1      | C1                     | САР                           | N/A     | 0805           | N/A               |

| 1      | C2                     | CAP (Css nom)                 | 0.82 nF | 0603           | FEC 301-9652      |

| 1      | C3                     | CAP(Css max)                  | 8.2 nF  | 0603           | FEC 301-9718      |

| 1      | C4                     | CAP (Css min)                 | 0.1 nF  | 0603           | FEC 722-110       |

| 1      | C5                     | CAP+                          | 100 μF  | CAP_ELEK_8MM   | FEC 319-9204      |

| 1      | C6                     | CAP                           | N/A     | 805            | N/A               |

| 1      | C7                     | CAP (C <sub>TIMER</sub> typ)  | 82 nF   | 603            | FEC 301-9550      |

| 1      | C8                     | CAP (CTIMER max)              | 690 nF  | 805            | FEC 335-2055      |

| 1      | С9                     | CAP (CTIMER min)              | 6.8 nF  | 603            | FEC 722-224       |

| 1      | C10                    | САР                           | 1 μF    | 805            |                   |

| 1      | C11                    | CAP                           | 0.1 μF  | Taj-C          | N/A FEC           |

| 2      | R1, R3                 | RES                           | 39 kΩ   | 805            | 912-049           |

| 4      | R2, R4, R6, R7         | RES                           | 1 kΩ    | 805            | FEC 911-859       |

| 1      | R5                     | RES                           | 82 kΩ   | 805            | FEC 360-1950      |

| 1      | R8                     | RES                           | 1.8 kΩ  | 805            | FEC 360-1754      |

| 1      | R9                     | RES                           | N/A     | 805            |                   |

| 1      | R10                    | RES (R <sub>DRAIN</sub> A)    | 2.2 ΜΩ  | 805            | FEC360-2126       |

| 1      | R11                    | RES (R <sub>DRAIN</sub> B)    | 10 MΩ   | 805            | FEC 360-2205      |

| 1      | R12                    | RES (R <sub>SHUNTNOM</sub> )  | 39 kΩ   | 1206           | FEC 360-1158      |

| 1      | R13                    | RES (R <sub>SHUNT</sub> B)    | 22 kΩ   | 1206           | FEC 513-246       |

| 1      | R14                    | RES                           | N/A     | 1206           |                   |

| 1      | R15                    | RES                           | N/A     | 1206           |                   |

| 1      | R16                    | RES                           | N/A     | 1206           |                   |

| 1      | R17                    | RES                           | 10 kΩ   | 805            | FEC 360-1845      |

| 1      | R18                    | RES                           | 22 kΩ   | 805            | FEC 360-1882      |

| 1      | R19                    | RES                           | 2.2 kΩ  | 805            | FEC 360-1766      |

| 1      | R20                    | RES (R <sub>TIMER</sub> user) | N/A     | 805            |                   |

| 1      | R21                    | RES (RTIMER NOM)              | 1.5 MΩ  | 805            | FEC 360-2102      |

| 1      | R22                    | RES (RTIMER max)              | 15 ΜΩ   | 805            | FEC 335-2481      |

| 1      | R23                    | RES (RTIMER MIAX)             | 150 kΩ  | 805            | FEC 360-1985      |

|        |                        |                               |         |                |                   |

| 5      | R24-R28                | RES                           | 470 Ω   | 805            | FEC 196-230       |

| 1      | RSENSE                 | RES                           | 33 mΩ   | 1206           | FEC 156-220       |

| 1      | Q1                     | IRFR3910                      |         | DPAK           | FEC 706-486       |

| 1      | Q2                     | SI2308DS                      |         | SOT23 3-PIN    | FEC 334-5245      |

| 2      | D1, D2                 | DIODE                         |         | DO35           | FEC 505-950       |

| 2      | D3, D4                 | LED                           |         | LED SMT Yellow | FEC 515-619       |

| 2      | D5, D6                 | LED                           |         | LED SMT Green  | FEC 515-620       |

| 1      | D7                     |                               |         | LED SMT Red    | FEC 515-607       |

| 1      | D8                     | ZENER DIODE                   |         | SOT23 3-PIN    | FEC 931-550       |

| 2      | S1, S2                 | SW-PUSH-SMD                   |         | SW_PB_SMD_6MM  | FEC 177-807       |

| 2      | S3, S8                 | DIL SW 4WAY                   |         | DIL            | FEC 312-680       |

| 1<br>2 | S4                     | DIL SW 6WAY                   |         | DIL            | FEC 312-691       |

|        | S5, S6                 | DIL SW 8WAY                   |         | DIL            | FEC 312-708       |

| 1      | S7                     | DIL SW 10WAY                  |         | DIL            | FEC 312-710       |

| Qty | <b>Ref Description</b> | Part Type      | Value | Part Decal               | Part No.    |

|-----|------------------------|----------------|-------|--------------------------|-------------|

| 2   | J1, J10                | BANANA         |       | BANANA BLACK             | FEC 150-040 |

| 4   | J2–J4, J6              | BANANA         |       | BANANA BLUE              | FEC 150-042 |

| 3   | J5, J7, J11            | SMB            |       | SMB                      | FEC 310-682 |

| 2   | J8, J9                 | CON\12P\ED\SKT |       | CON-12P-156-SRA          | S5061-ND    |

| 1   | J12                    | CON\PWR        |       | 3-way Term Block         | FEC 151-786 |

| 1   | J13                    | CON\PWR        |       | 2-way Term Block         | FEC 151-785 |

| 14  | T1–T14                 | TESTPOINT      |       | TESTPOINT BLACK          | FEC 240-333 |

| 1   | L1                     | JUMPER-4       |       | $2 \times 4$ -way Header | FEC 511-791 |

| 2   | L2-L3                  | JUMPER         |       | $1 \times 2$ -way Header | FEC 511-705 |

| 4   | L4–L7                  | JUMPER2\SIP3   |       | $1 \times 3$ -way Header | FEC 511-717 |

| 7   | L1–L7                  | Shorting Links |       | Shorting Links           | FEC 150-410 |

| 4   | Each Corner            | Stick-On Feet  |       | 3M                       | FEC 651-813 |

#### MICRO EVALUATION BOARD BILL OF MATERIALS Table 7.

| Qty | <b>Ref Description</b> | Part Type                    | Value                | Part Decal        | Part No.     | Source  |

|-----|------------------------|------------------------------|----------------------|-------------------|--------------|---------|

| 1   | U1                     | ADM1073ARU                   |                      | 14-TSSOP          | ADM1073      | ADI     |

| 1   | C1                     | CAP (CTIMER nom)             | 82 nF                | 603               | FEC 301-9550 | FARNELL |

| 1   | C2                     | CAP (Css nom)                | 0.82 nF              | 0603              | FEC 301-9652 | FARNELL |

| 1   | C3                     | CAP                          | N/A                  | 603               | N/A          | N/A     |

| 2   | R1, R3                 | RES                          | 39 kΩ                | 805               | FEC 912-049  | FARNELL |

| 2   | R2, R4                 | RES                          | 1 kΩ                 | 805               | FEC 911-859  | FARNELL |

| 4   | R5, R14, R15, R16      | RES                          | 8.2 kΩ               | 1206              | FEC 360-1110 | FARNELL |

| 1   | R6                     | RES                          | 0 Ω                  | 805               | FEC 758-413  | FARNELL |

| 1   | R7                     | RES (R <sub>TIMER</sub> nom) | 1.5 MΩ               | 805               | FEC 360-2102 | FARNELL |

| 5   | R8–R12                 | RES                          | 470 Ω                | 805               | FEC 196-230  | FARNELL |

| 1   | R13                    | RES (R <sub>DRAIN</sub> )    | 10 MΩ                | 805               | FEC 360-2205 | FARNELL |

| 1   | RDROP                  | RES (R <sub>SHUNTNOM</sub> ) | 39 kΩ                | 1206              | FEC 360-1158 | FARNELL |

| 1   | RSENSE                 | RES                          | $33\mathrm{m}\Omega$ | 1206              | FEC 156-220  | FARNELL |

| 1   | Q1                     | IRFR3910                     |                      | DPAK              | FEC 706-486  | FARNELL |

| 2   | D3, D4                 | LED                          |                      | LED SMT Yellow    | FEC 515-619  | FARNELL |

| 2   | D5, D6                 | LED                          |                      | LED SMT Green     | FEC 515-620  | FARNELL |

| 1   | D7                     | LED                          |                      | LED SMT Red       | FEC 515-607  | FARNELL |

| 1   | D8                     | ZENER DIODE                  |                      | SOT23 3-PIN       | FEC 931-550  | FARNELL |

| 2   | S1, S2                 | SW-PUSH-SMD                  |                      | Pushbutton Switch | FEC 535-930  | FARNELL |

| 1   | J1                     | CON\PWR                      |                      | 3-way Term Block  | FEC 151-786  | FARNELL |

| 1   | J2                     | CON\PWR                      |                      | 3-way Term Block  | N/A          | FARNELL |

| 1   | J3                     | CON\PWR                      |                      | 2-way Term Block  | N/A          | FARNELL |

#### **ORDERING GUIDE**

| Model           | Package Description                                           |

|-----------------|---------------------------------------------------------------|

| EVAL-ADM1073EB  | Main Evaluation Board and Micro Evaluation Board <sup>1</sup> |

| EVAL-ADM1073MEB | Micro Evaluation Board only                                   |

<sup>1</sup> Includes Main Evaluation Board for bench evaluation and Micro Evaluation Board for in-system evaluation.

### NOTES

# NOTES

© 2004 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D04582-0-9/04(0)

www.analog.com

Rev. 0 | Page 20 of 20